Del 08-05-2017 al 10-05-2017

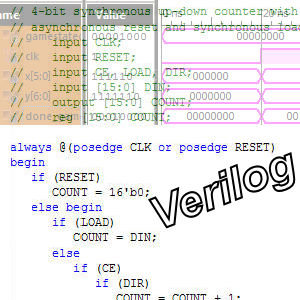

Diseñando con Verilog. Síntesis Lógica y Simulación para FPGAs de Xilinx

VRLG01: Designing with Verilog. Logical Synthesis and Simulation for Xilinx FPGA design

Este curso es una introducción completa al lenguaje de Verilog. El énfasis está en escribir código a nivel RTL (Transferencia de Registro) y escribir código comportamental. Éste curso aborda específicamente los dispositivos Xilinx y los dispositivos FPGA en general. La formación puede aplicarse a cualquier diseño digital utilizando un enfoque top-down. Este curso combina conceptos teoricos con ejercicios prácticos de laboratorio para reforzar conceptos clave. También aprenderá técnicas avanzadas de codificación que mejorarán su optimización FPGA. Este curso cubre Verilog 1995 y 2001. En este curso de tres días, obtendrá valiosa experiencia práctica. Los estudiantes con poco o ningún conocimiento de Verilog terminarán este curso con la habilidad de escribir diseños de hardware eficientes y realizar simulaciones de alto nivel de HDL.

En el enlace más abajo puede encontrar los detalles del curso (VRLG01). Adicionalmente en el siguiente enlace puede ver la planificación en cursos Xilinx para el segundo semestre de 2017 (aquí).

Fechas:

- VRLG01: Diseñando con Verilog. Síntesis Lógica y Simulación para FPGAs de Xilinx.

- Lunes 8, martes 9 y miércoles 10 de mayo de 2017 de 9 a 18 hs

Lugar:

Escuela Politécnica Superior de la Universidad Autónoma de Madrid. (Cómo llegar).

Fundación Tripartida

Recuerde que su empresa puede beneficiarse de las subvenciones de la fundación tripartita.