Seminario online: Del Edge al Alto Rendimiento – Explorando Spartan UltraScale+ y Kintex UltraScale+ Gen2

Presentación (In English below):

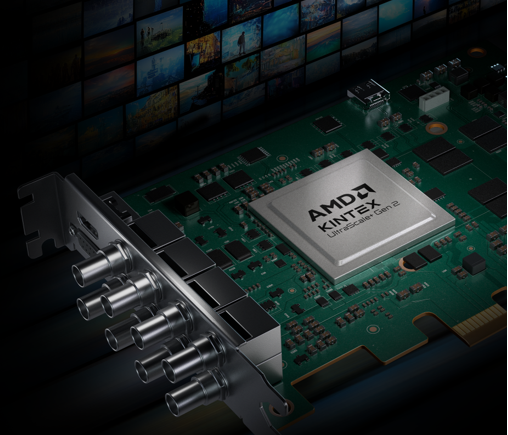

Este workshop online ofrece una introducción completa a las familias de FPGAs AMD Spartan UltraScale+ y Kintex UltraScale+ Gen2, centrándose en su arquitectura, posicionamiento y flujos prácticos de diseño. La sesión está dirigida a ingenieros que desean comprender cómo estos dispositivos cubren un amplio rango de aplicaciones, desde sistemas embebidos optimizados en coste hasta procesamiento de señal de alto rendimiento y aceleración de datos.

El workshop comienza con una visión general de la arquitectura UltraScale+ y de la nueva generación de dispositivos Kintex, destacando mejoras clave en densidad lógica, eficiencia energética e integración del sistema. Los participantes explorarán los principales componentes arquitectónicos, incluyendo recursos de lógica programable, bloques DSP, memorias, estructuras de reloj y interfaces de alta velocidad. Se hará especial énfasis en cómo Spartan UltraScale+ está orientado a aplicaciones sensibles al coste y al edge, mientras que Kintex UltraScale+ Gen2 permite diseños de mayor rendimiento y con altas demandas de ancho de banda.

En la segunda parte de la sesión, el enfoque se traslada al flujo de desarrollo utilizando Vivado ML Edition, cubriendo desde la entrada de diseño hasta la síntesis, implementación y validación en hardware. El workshop también introduce buenas prácticas para la utilización eficiente de recursos, cierre de timing y optimización de consumo, junto con recomendaciones para seleccionar el dispositivo más adecuado según la aplicación.

A lo largo del workshop, se utilizarán ejemplos de aplicaciones reales, como control industrial, visión embebida, comunicaciones y procesamiento de datos para ilustrar los compromisos de diseño y las decisiones arquitectónicas. La sesión finaliza con una breve demostración y un turno de preguntas en directo, asegurando que los participantes adquieran una comprensión clara de cómo comenzar a diseñar eficazmente con dispositivos Spartan UltraScale+ y Kintex UltraScale+ Gen2.

Introduction (In English):

This workshop provides a comprehensive introduction to AMD Spartan UltraScale+ and Kintex UltraScale+ Gen2 FPGA families, focusing on their architecture, positioning, and practical design workflows. The session is designed for engineers seeking to understand how these devices address a wide range of applications, from cost-optimized embedded systems to high-performance signal processing and data acceleration.

The workshop begins with an overview of the UltraScale+ and next-generation Kintex architectures, highlighting key improvements in logic density, power efficiency, and system integration. Participants will explore the main architectural components, including programmable logic resources, DSP slices, memory blocks, clocking structures, and high-speed interfaces. Special attention is given to how Spartan UltraScale+ targets cost-sensitive and edge applications, while Kintex UltraScale+ Gen2 enables higher performance and bandwidth-intensive designs.

In the second part of the session, the focus shifts to the development flow using Vivado ML Edition, covering design entry, synthesis, implementation, and hardware validation. The workshop also introduces best practices for resource utilization, timing closure, and power optimization, along with guidance on selecting the right device for specific use cases.

Throughout the workshop, real-world application examples such as industrial control, embedded vision, communications, and data processing are used to illustrate design trade-offs and architectural choices. The session concludes with a short demonstration and a live Q&A, ensuring participants leave with a clear understanding of how to effectively start designing with Spartan UltraScale+ and Kintex UltraScale+ Gen2 devices.

The seminar will be in Spanish.

Descriptores preliminares / Agenda (preliminary):

- Introduction & Context

- FPGA portfolio positioning: Spartan UltraScale+ (cost-optimized, edge), Kintex UltraScale+ Gen2 fits (performance, bandwidth)

- Architecture Overview. UltraScale+ architecture fundamentals

- Device Capabilities & Positioning. Performance vs power vs cost trade-offs

- Design Flow with Vivado ML. Toolchain overview

- Practical Design Considerations

- Q&A

Fecha / Date:

Jueves 21 de mayo de 2026 de 15:00 a 18:00h. (horario coordinado Europeo de verano)

Thursday, May 21st 2026 15:00 – 18:00 CEST.

Lugar de realización / Place:

Live on Line